Los circuitos combinatorios que se utilizan para restar dos números binarios se llaman Sustractores. Cuando los números binarios a restar son de bits simples, entonces, podemos utilizar un medio sustractor para realizar la tarea mientras que si necesitamos restar tres números binarios de bits simples (entre los cuales dos serán generalmente entradas mientras que el otro será el préstamo), tendremos que utilizar el sustractor completo. ¿Y qué pasa si deseamos restar dos números binarios de n-bits? Este es el caso que exige el uso de n-bit sustractor paralelo.

Estructura del sustractor paralelo

Generalmente cuando se necesita restar el número binario 2 del número binario 1, entonces el número binario 2 se expresará en su 2s complemento y luego se agrega con el número binario 1 (nada más que 2s complementan la forma de sustracción binaria).

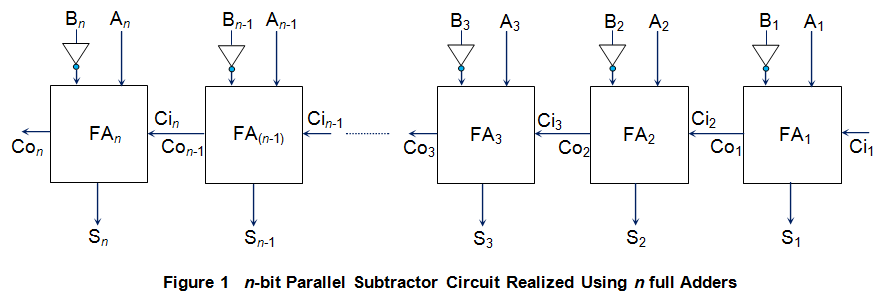

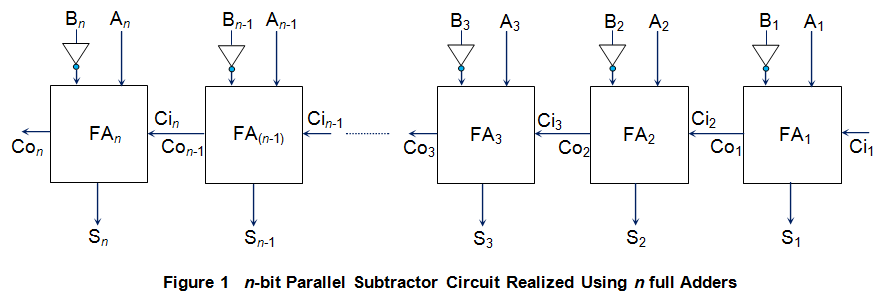

A continuación, se puede obtener un complemento de 2s de un número tomando 1s complemento del número y luego añadiendo 1 a su bit menos significativo (LSB). Además, tomar el complemento de 1s no significa nada más que negar el número binario. De la discusión presentada, se puede concluir que para realizar la resta, se puede utilizar el mismo circuito que para la suma (más sobre esto en el artículoVíbora paralela) siempre y cuando tengamos el número a restar en su forma de complemento de 2s. Esta tarea de expresar el número en 2s complemento puede lograrse mediante el primer uso de NO las puertas para invertir los bits en el número binario. Sin embargo, para sumar 1 en LSB, se puede hacer uso del primer sumador en la secuencia de n víboras completas utilizado en el circuito sólo por proporcionar la lógica alta en su llevar en (Ci1) pin. Como resultado, uno puede diseñar el n-bit sustractor paralelo como se muestra en la figura 1.

Aquí el número binario

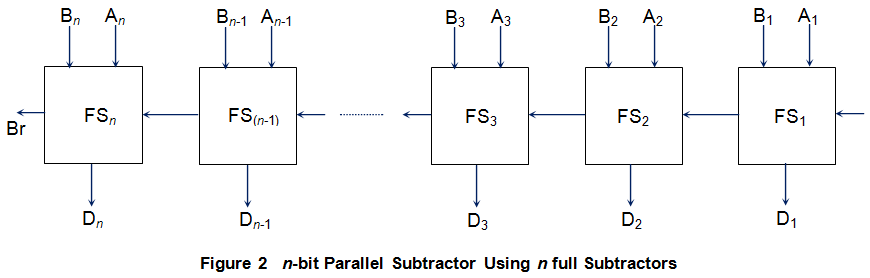

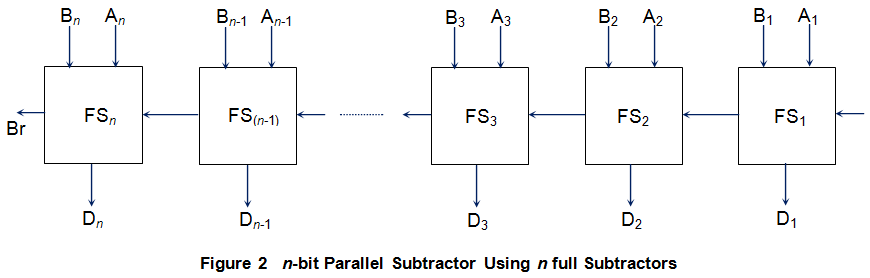

Aparte de este tipo de circuito, uno puede incluso diseñar el sustractor paralelo usando sólo una serie de sustractores completos en cascada. La figura 2 muestra dicho sustractor paralelo de un bit diseñado utilizando n sustractores completos (FS1 a FSn) unidos de una manera similar a la del caso de la víbora paralela n-bit.

El funcionamiento de tal circuito es sencillo y es muy similar al de un víbora paralela. Como resultado, incluso sustractores paralelos son propensos al efecto de la propagación de las ondas que da lugar a la salida retardada. Es decir, si el trato asociado a cada uno de los sustractores completos es T segundos, entonces los bits de diferencia global (D1D2Dn) y pedir prestado un poco (Br) se obtienen sólo después de n T segundos.