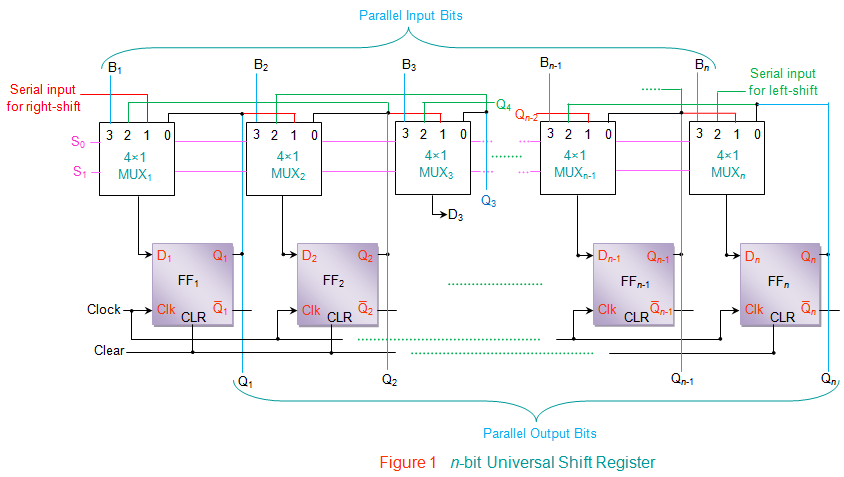

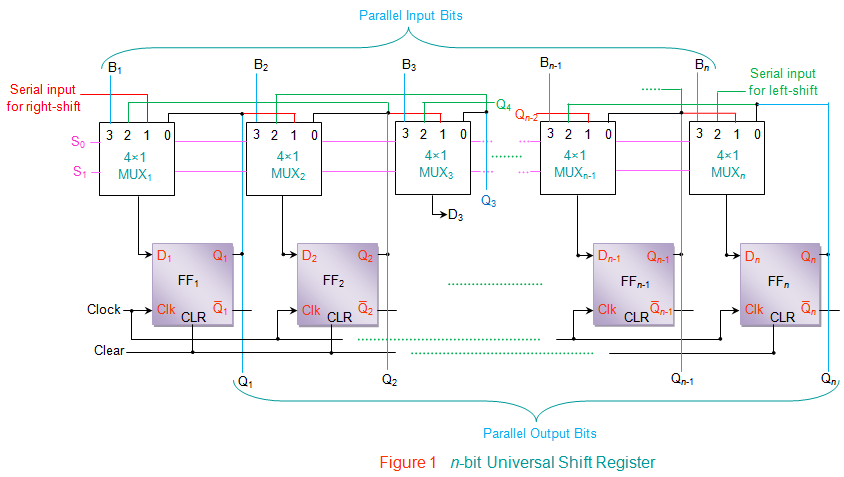

Registro de cambios universales es un registro que puede ser configurado para cargar y/o recuperar los datos en cualquier modo (ya sea en serie o paralelo) desplazándolo hacia la derecha o hacia la izquierda. En otras palabras, un diseño combinado de bits de datos unidireccionales (ya sea hacia la derecha o hacia la izquierda como en el caso de SISO, SIPO, PISO, PIPO) y registro de desplazamiento bidireccional junto con la provisión de carga paralela se denomina registro de cambio universal. Tal registro de cambio capaz de almacenar n bits de entrada se muestra en la figura 1.

El diseño mostrado en la figura 1 utiliza n 41 multiplexores para accionar los pines de entrada de n chancletas en el registro, que también están conectados a las entradas de reloj y claro. Todos los multiplexores en el circuito comparten las mismas líneas selectas, S1 y S0 (líneas rosas en la figura), para seleccionar el modo en que funcionan los registros de desplazamiento. También se ve que la MUX que conduce un determinado flip-flop tiene su

- La primera entrada (Pin Número 0) conectada al pin de salida del mismo flip-flop, es decir, ceroth alfiler de MUX1 está conectado a Q1…cero…th alfiler de MUX2 está conectado a Q2…cero…th alfiler de MUXn está conectado a Qn.

- La segunda entrada (Pin Número 1) conectada a la salida del muy anterior flip-flop (excepto el primer flip-flop FF1 donde actúa como una entrada en serie a los bits de datos de entrada que deben ser desplazados hacia la derecha), es decir, el primer pin de MUX2 está conectado a Q1…el primer alfiler de MUX…3 está conectado a Q2…el primer alfiler de MUX…n está conectado a Qn-1.

- Tercera entrada (Pin Número 2) conectada a la salida del siguiente flip-flop (excepto el primer flip-flop FFn donde actúa como una entrada en serie a los bits de datos de entrada que se deben desplazar hacia la izquierda) es decir, el segundo pin de MUX1 está conectado a Q2…el segundo pin de MUX…2 está conectado a Q3…el segundo pin de MUX…n-1 está conectado a Qn.

- Cuarta entrada (Pin Número 3) conectada a los bits individuales de la palabra de datos de entrada que debe ser almacenada en el registro, proporcionando así la facilidad de carga en paralelo.

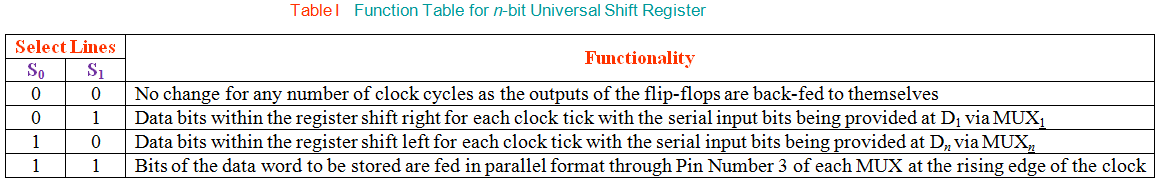

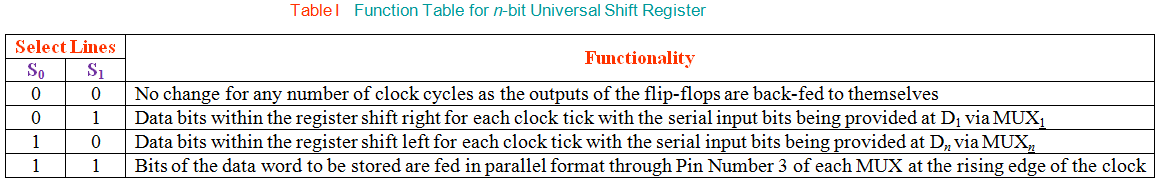

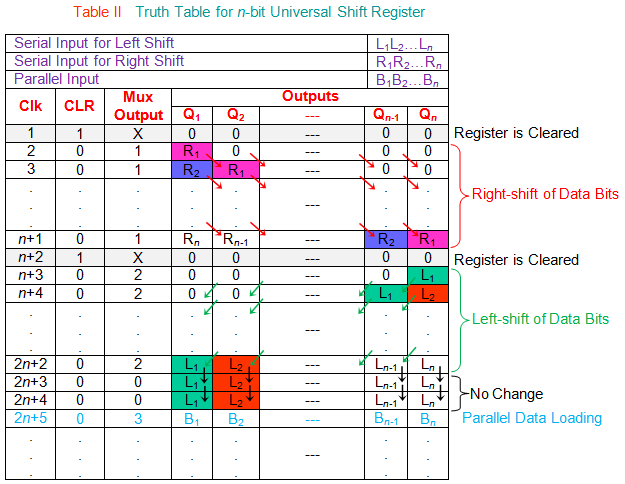

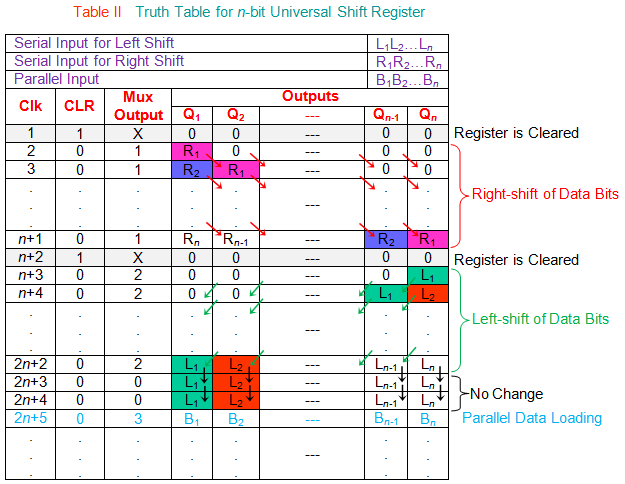

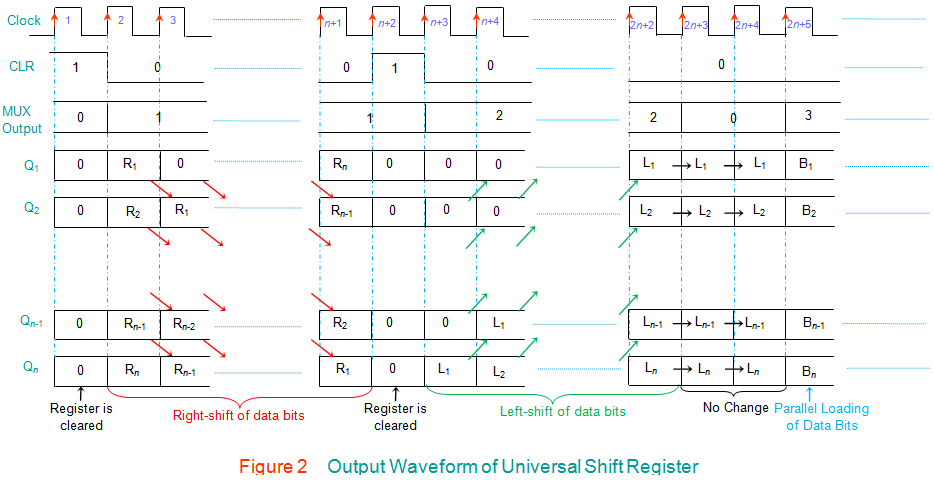

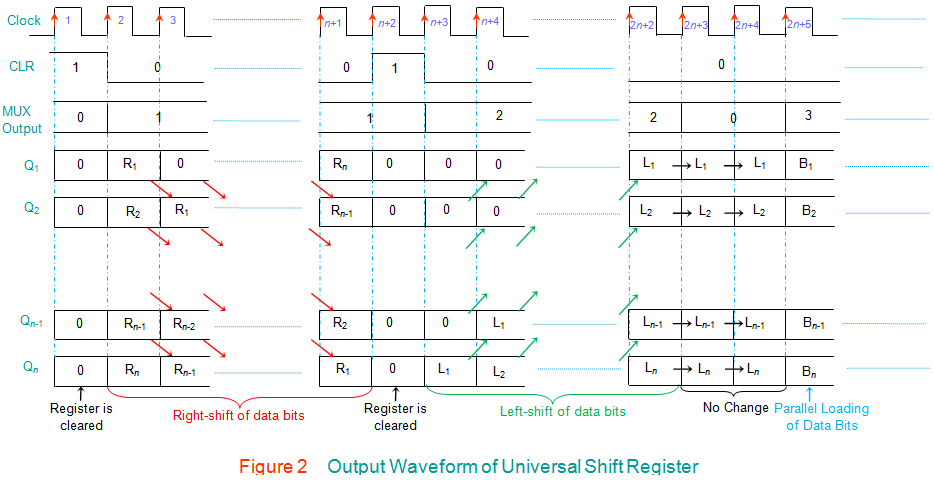

El funcionamiento de este registro de cambio se explica en la Tabla I. El correspondiente tabla de la verdad y las formas de onda están dadas por la Tabla II y la Figura 2, respectivamente.