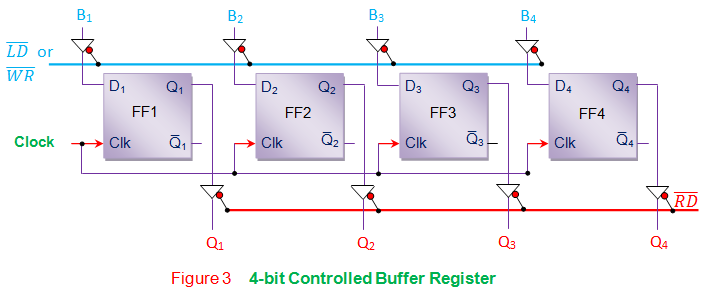

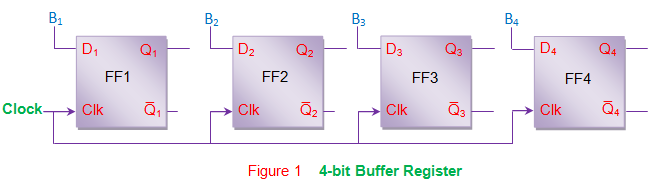

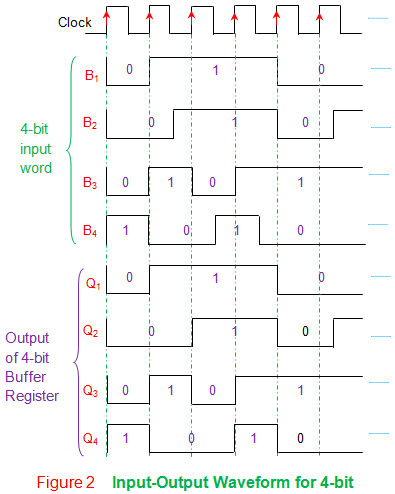

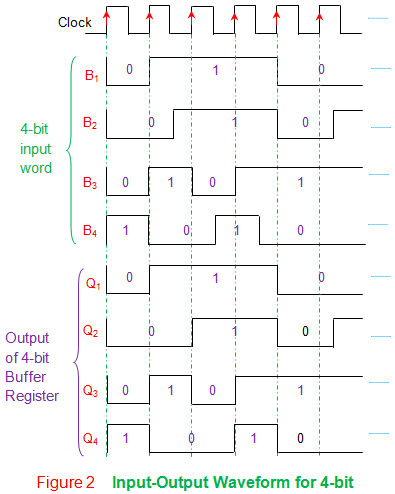

Registros de la memoria intermedia son un tipo de registros utilizados para almacenar una palabra binaria. Estos pueden ser construidos usando una serie de chanclas ya que cada chancleta puede almacenar un solo trozo. Esto significa que para almacenar una palabra binaria de n-bit uno debe diseñar una serie de n chancletas. La figura 1 muestra un registro de búfer sincrónico de 4 bits formado por la cascada de cuatro bordes positivos disparados Chancletas D. Aquí la palabra de datos de entrada entera B1B2B3B4 se carga en el registro con un solo tictac de reloj. Esto significa que en cada borde de entrada del reloj los valores de las salidas de los flip-flop siguen sus bits de entrada, es decir, Q1 = B1, Q2 = B2, Q3 = B3 y Q4 = B4 como se muestra en la figura 2.

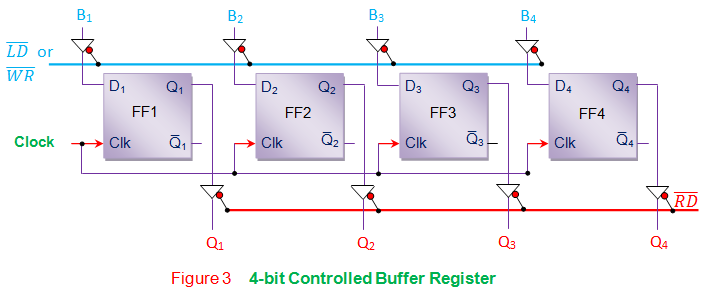

Registros de la memoria intermedia no ofrecen ningún medio de control sobre las entradas, lo que a su vez conduce a salidas no controladas. Para superar este inconveniente se puede recurrir a los registros de memoria intermedia controlados, como se muestra en la figura 3.

En este diseño, se utilizan interruptores triestatales para controlar el funcionamiento de la carga y/o la recuperación de los datos hacia/desde el registro de la memoria intermedia. Aquí uno tiene que tirar de la