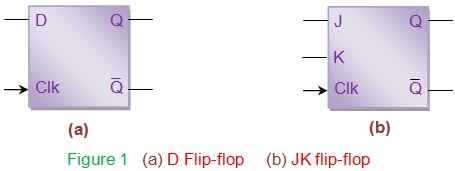

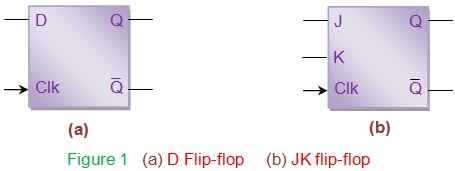

El contador es un circuito electrónico que se utiliza para contar el número de veces que ocurre un evento. En electrónica digital Los contadores se construyen utilizando series de chanclas. Aunque cualquier chancleta puede conectarse adecuadamente para formar un contador, las más utilizadas son la D y la Chancletas JK (Figura 1).

Como es sabido, las chancletas son dispositivos biestatales, lo que significa que tienen dos estados, o bien cero (0) o uno (1). Así, una sola chancleta puede seguir una cuenta de dos, es decir, cuenta de 0 a 1 y por lo tanto se llama contador de módulo-2 (mod-2).

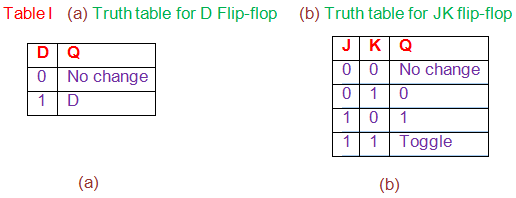

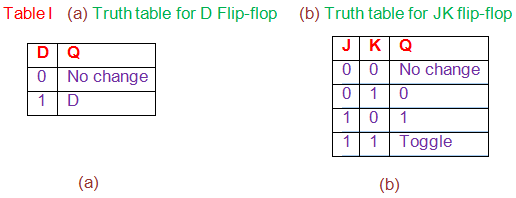

Por los mismos motivos, se puede esperar que dos chancletas conectadas en serie formen un contador de 2 bits que cuente de 0 a 3 y que comprenda 4 estados, por lo que se puede denominar contador mod-4. Generalizando, se obtiene un contador de n-bit o mod-n de 2n estados que cuentan de 0 a (2)n-1) por la cascada de n chanclas. Sin embargo, para comportarse como contadores, las chancletas deben ser impulsadas por alto (estado lógico 1) en sus entradas, tanto en el caso de los tipos D como JK. La razón de esto puede ser entendida por el tablas de verdad dada por la Tabla I.

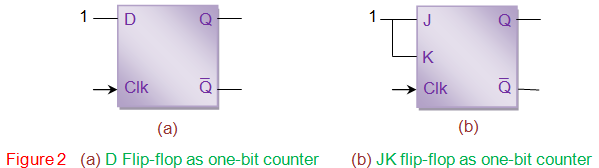

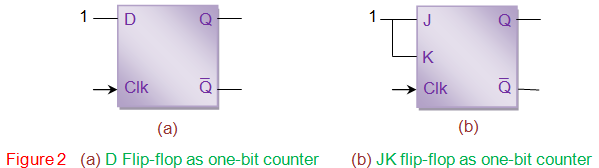

Considerando D flip-flopse puede ver que la salida cambia sólo cuando la entrada es alta. De manera similar para JK flip-flop El estado de salida permanece sin cambios (para J = K = 0) o fijado en un valor determinado (0 para J = 0 y K = 1; 1 para J = 1 y K = 0) para todos los casos se espera cuando ambos son altos. En los contadores se espera que el estado cambie y no permanezca atado a un valor particular. Por lo tanto, cuando se impulsa 1 en las entradas de estas chancletas, actúan como contadores de 1 bit (Figura 2).

Las características del contador están determinadas por el modo de interconexión entre las chancletas. Los contadores pueden ser

- Asíncrono o síncrono,

- Contadores ascendentes o descendentes y/o

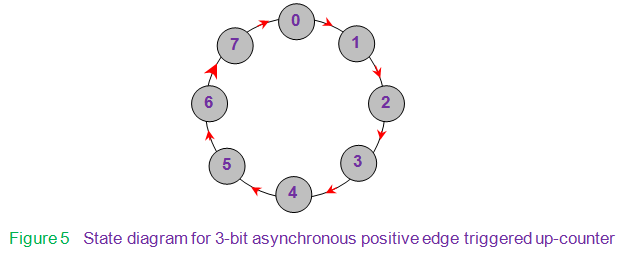

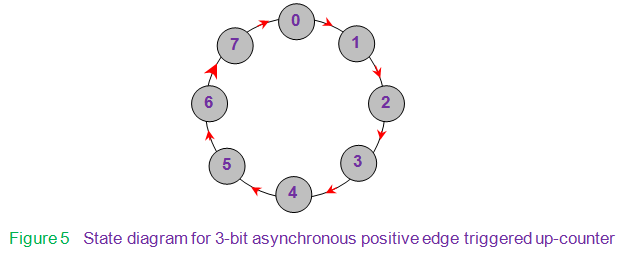

- Flanco positivo o negativo disparado dependiendo de la conexión proporcionada en la entrada del reloj de las chancletas. El comportamiento de un contador puede explicarse a través de un diagrama de tiempo (formas de onda), tabla de verdad y/o diagramas de estado.

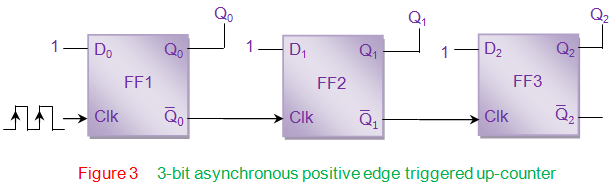

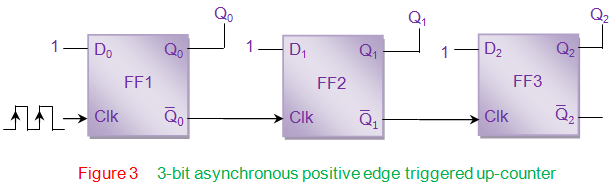

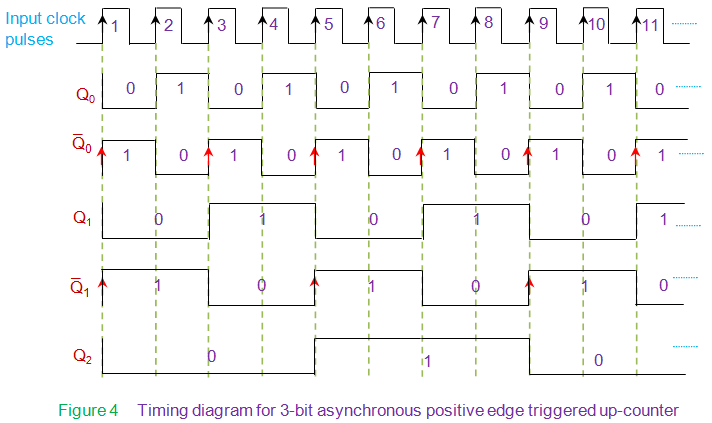

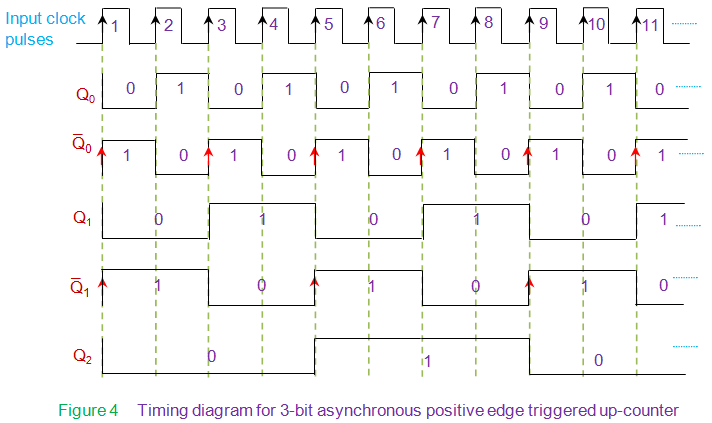

La figura 3 muestra un contador ascendente asíncrono de 3 bits formado por tres chanclas D en cascada de bordes positivos. Aquí todas las entradas (D0, D1 y D2) se hacen altas. La entrada de reloj del flip-flop 1 (FF1) es impulsada por pulsos de reloj externos mientras que los del segundo y tercero (FF2 y FF3) son impulsados por

Asumamos que el estado inicial del contador es Q2Q1Q0 = 111, sólo para entender el funcionamiento del contador. En este caso, para el primer pulso de reloj Q0 cambia de 1 a 0. Esto implica que el

Luego para el borde de ataque del segundo pulso de reloj Q0 de nuevo cambia de 0 a 1, lo que implica

En general vemos que para un contador de n-bits parecido al de la figura 3, bajar la mayoría de los bits (LSB) = 2o conmuta para cada ciclo de reloj, mientras que los siguientes bits más altos conmutan sólo cuando sus bits precedentes cambian su estado de 1 a 0. Por ejemplo, Q2 en el contador ascendente de 3 bits cambia su estado sólo cuando Q1 cambia de 1 a 0 (que no es más que

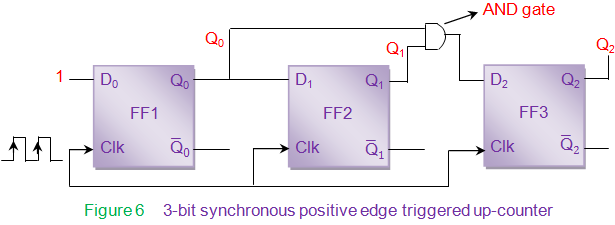

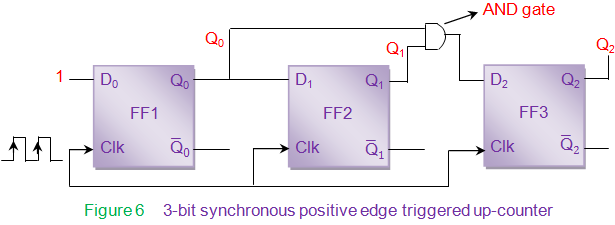

El efecto dominó de los contadores asíncronos plantea un problema cuando los retardos de propagación se asocian a las chancletas. Para superar esto, los contadores están diseñados de tal manera que las entradas de reloj de todas las chancletas que forman el contador son impulsadas por el mismo tren de pulsos de entrada de reloj. Estos se denominan contadores síncronos (Figura 6). Esto hace que todas las chancletas cambien de estado simultáneamente eliminando el retardo que se produce en el caso de los contadores asíncronos.

En la figura 6 se observa que todas las entradas de las chancletas no son impulsadas a gran altura como en el caso del contador asíncrono (figura 3). En el caso de los contadores síncronos, las conexiones a los pines de entrada de las flip-flop (D0 de FF1, D1 de FF2 y D2 de FF3) se deciden dependiendo de la secuencia de estados que espera el contador. Como el contador que se muestra en la figura x es análogo a su contraparte que se muestra en la figura 3, el número de estados y la transición entre los estados sigue siendo el mismo. Por lo tanto, el diagrama de estados y la tabla de verdad permanecen inalterados. Por lo tanto, se puede llegar a la unidad de los bits de entrada analizando la Tabla II para encontrar las condiciones requeridas para que los bits de salida se conmuevan.

Como es evidente en la tabla, el bit Q0 se requiere para conmutar por cada transición de borde positivo en el pulso del reloj de entrada. Por lo tanto, la clavija de entrada D0 …debe ser llevado a lo alto. Sin embargo, el bit Q1 necesita transitar sólo cuando el bit Q0 es 1, indicado por las flechas azules en la Tabla II. Esto puede lograrse conectando Q0 como la entrada al FF2. Además, también se observa que Q2 tiene que cambiar su estado sólo si ambos Q1 y Q0 son altas como se muestra en las flechas verdes de la Tabla II. Para lograr esta condición, es necesario hacer uso de dos entradas Y la puerta impulsado por los bits Q0 y Q1. Esto se debe al hecho de que la salida de la puerta Y es alta sólo cuando todas sus entradas son altas. Ahora el contador mostrado en la figura 6 funciona como un contador ascendente que cuenta de 0 a 7 incrementando en uno por cada pulso de reloj de entrada.

En general, en un contador ascendente síncrono de n bits, el LSB debe conmutar por cada transición de borde positivo en el pulso del reloj de entrada; el siguiente bit superior necesita cambiar su estado sólo cuando su bit precedente (= LSB) es alto; el siguiente bit superior tiene que transitar sólo si sus dos bits precedentes son altos y así sucesivamente. Así, en caso de contador sincrónico los flip-flop cambian de estado sólo cuando las salidas de todos los flip-flop precedentes están altas. Para ello, hay que conectar la salida de las compuertas AND para accionar los pines de entrada de cada flip-flop. Más adelante en cada etapa estas compuertas Y se requieren lógicamente y los bits de salida de todos los chanclas.

El funcionamiento de los contadores descendentes es casi similar al de los contadores ascendentes, excepto por el hecho de que la secuencia de conteo será de alta a baja disminución de uno por cada pulso de reloj. o por ejemplo, conteos descendentes de 3 bits de 7 (111) a 0 (000) y no de 0 a 7. Así pues, en el caso de un contador asíncrono hay que considerar la transición de los bits de salida de 0 a 1 en lugar de 1 a 0. De manera similar, en el caso de los contadores síncronos Y las compuertas se deben utilizar para

Además de los contadores básicos de subida y bajada, también existen otros tipos especiales de contadores como Contador de anillos, Contador de Johnson, Contador de Décadas, Contador de Modificaciones y así sucesivamente. Además, ligeras modificaciones en el diseño del contador propuesto producirían variaciones como

- Añadiendo una línea de control para seleccionar el conteo ascendente o descendente se realiza un conteo ascendente/ descendente,

- El uso de clavijas claras y preestablecidas de las chancletas permite establecer el estado inicial del contador

- La adición de una lógica adecuada lleva a romper la secuencia de conteo antes del 2n estados han transcurrido, es decir, se puede hacer que un contador de 3 bits cuente sólo hasta 5 y se puede hacer que repita la secuencia (contador Mod-6). Sin embargo, hay que señalar que aunque el diseño de cada uno de ellos difiere en cierta medida, el principio básico de funcionamiento de todos ellos sigue siendo el mismo.