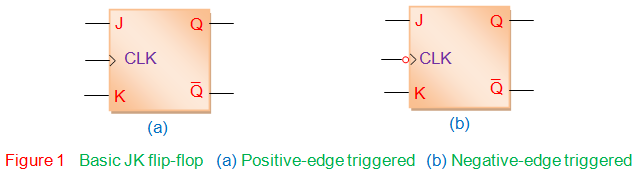

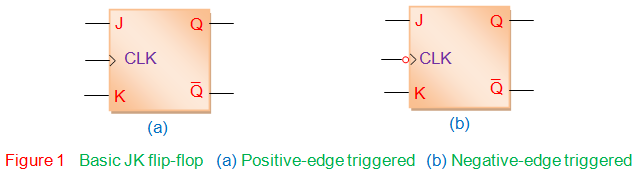

JK flip-flop es un dispositivo de memoria secuencial biestatal de un solo bit llamado así por su inventor por Jack Kil. En general tiene un pin de entrada de reloj (CLK), dos pines de entrada de datos (J y K) y dos pines de salida (Q y Q) como muestra la figura 1. El flip-flop JK puede ser activado en el borde de entrada del reloj o en su borde de salida y por lo tanto puede ser activado en el borde positivo o negativo, respectivamente.

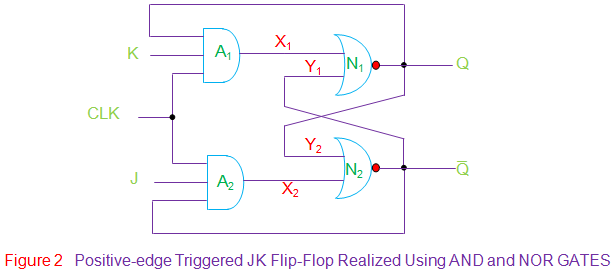

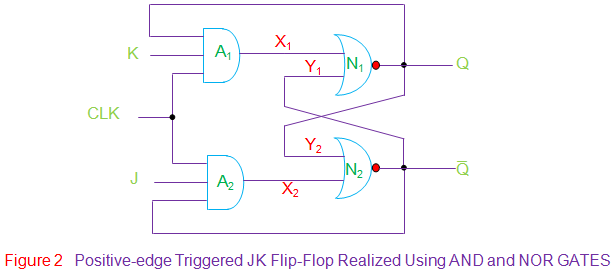

Para tener una idea del funcionamiento de la chancleta JK, hay que realizar interms de puertas básicas similares a la de la figura 2, que expresa un borde positivo disparado JK flip-flop usando Y las puertas y Puertas NOR. Aquí se ve que la salida Q es lógicamente yed con la entrada K y el pulso de reloj (usando la puerta AND 1, A1) mientras que la salida Q es andada con la entrada J y el pulso de reloj (usando la puerta AND 2, A2).

Además, la salida de A1 se alimenta como una de las entradas (X1) a la puerta NOR 1, N1 cuya otra entrada (Y1) está conectada a la salida Q. De manera similar, la puerta 2 de NOR, N2 tiene sus dos entradas (X2 y Y2) como salida de A2 y la salida Q (respectivamente).

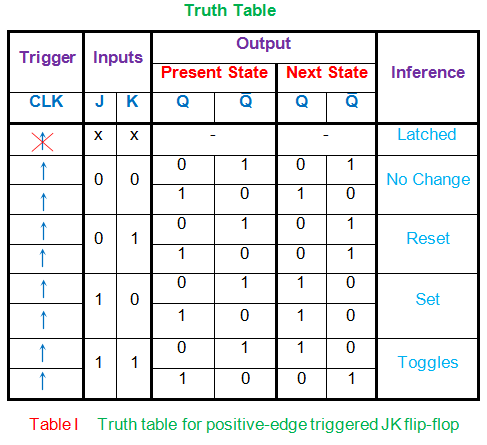

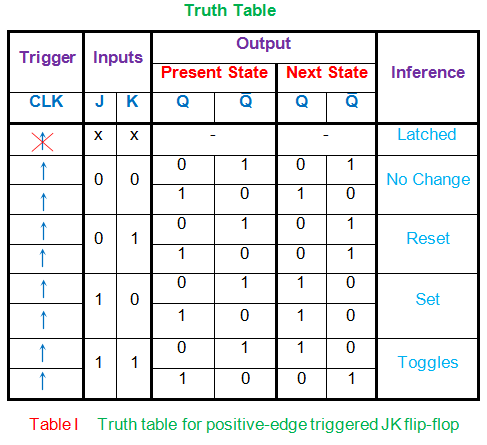

Inicialmente dejemos que J = K = 0, Q = 0 y Q = 1. Ahora consideremos la aparición del borde positivo del primer pulso de reloj en la clavija CLK del flip-flop. Esto resulta en X1 = 0 y X2 = 0. Entonces la salida de N1 se convertirá en 0 como X1 = 0 y Q = 1; mientras que la salida de N2 se convertirá en 1 como X2 = 0 y Q = 0. Así se obtiene Q = 0 y Q = 1. Sin embargo, si se considera que los estados iniciales son J = K = 0, Q = 1 y Q = 0, entonces X1 = X2 = 0, lo que resulta en Q = 1 y Q = 0. Esto indica que el estado de las salidas de las chancletas Q y Q permanece sin cambios para el caso de J = K = 0.

Ahora supongamos que J = 0, K = 1, Q = 0 y Q = 1. Analizando sobre la misma base, se obtiene X1 = X2 = 0, lo que resulta en Q = 0 (y por lo tanto Q = 1). En el mismo caso, si Q y Q son 1 y 0, respectivamente, entonces X1 = 1 y X2 = 0, lo que resultaría en Q = 0 (y por lo tanto Q = 1). Esto implica que si J = 0 y K = 1, entonces la chancleta se restablece (Q = 0 y Q = 1).

A continuación, si J = 1, K = 0, Q = 1 y Q = 0, entonces X1 = X2 = 0 que resulta en Q = 1 (y por lo tanto Q = 0). En el mismo caso, si Q = 0 y Q = 1, entonces X1 = 0, X2 = 1 que lleva a Q = 0 y por lo tanto Q es forzado al valor 1. Esto significa que para el caso de J = 1 y K = 0, la salida del flip-flop siempre estará fijada, es decir, Q = 1 y Q = 0.

De manera similar para J = 1, K = 1, Q = 1 y Q = 0 se obtiene X1 = 1, X2 = 0 y Q = 0 (y por lo tanto Q = 1); y si Q cambia a 0 y Q a 1, entonces X1 = 0, X2 = 1 que fuerza Q a 0 y por lo tanto Q a 1. Esto indica que para J = K = 1, las salidas de los flip-flop conmutan lo que significa que Q cambia de 0 a 1 o de 1 a 0, y estos cambios se reflejan en la clavija de salida Q en consecuencia.

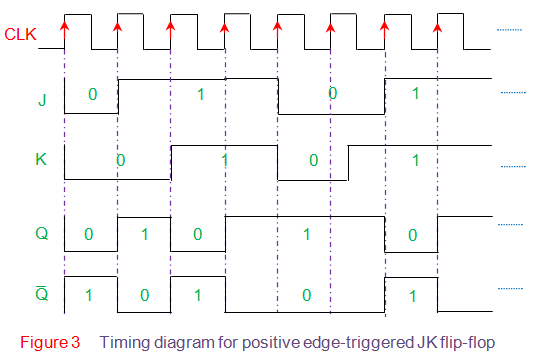

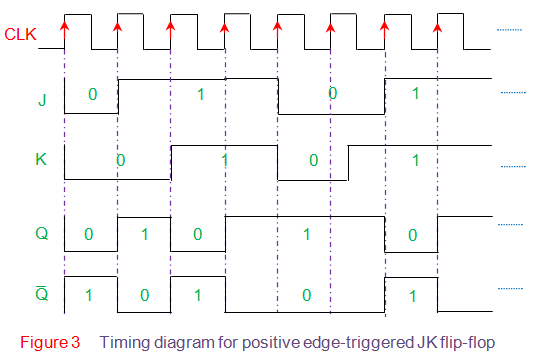

Sin embargo, cabe señalar que el estado de las chanclas permanece inalterado si no hay un borde ascendente del reloj en su entrada. Todos estos detalles se pueden resumir como en la Tabla I. Las formas de onda correspondientes a las mismas se presentan en la figura 3. Además, hay que señalar que el funcionamiento de la chancleta activada por el borde negativo es similar al de la activada por el borde positivo, salvo que los cambios se producen en el borde de salida del impulso del reloj en lugar de su borde inicial.

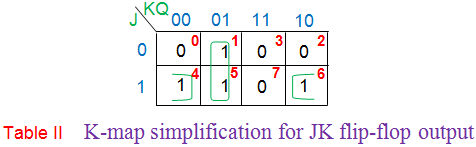

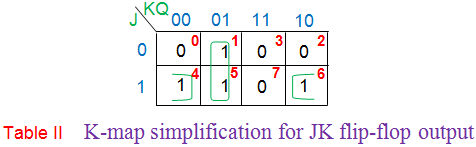

De la tabla de verdad de arriba se puede llegar a la ecuación para la salida del J K flip-flop como (Tabla II)

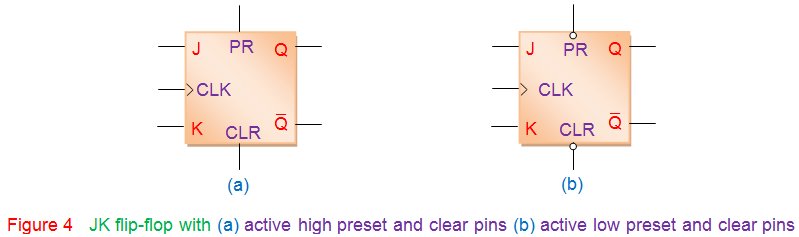

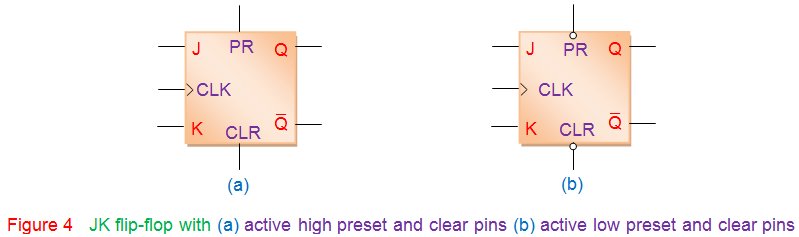

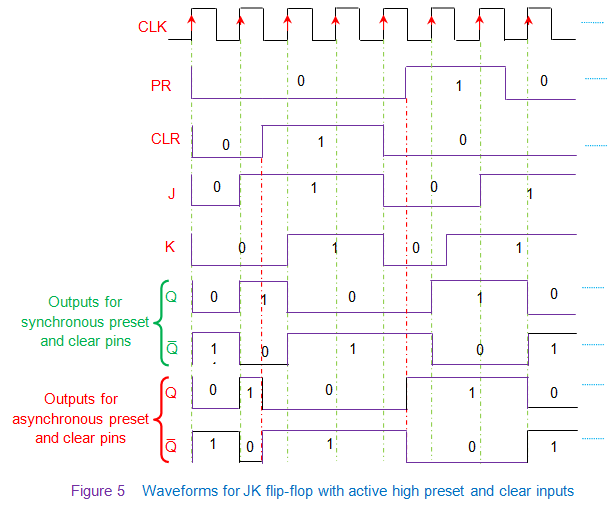

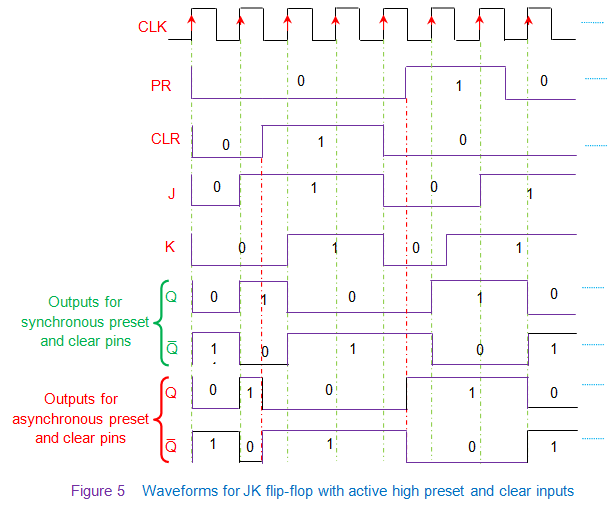

Además de los pines básicos de entrada y salida que se muestran en la figura 1, J K flip-flop también puede tener entradas especiales como claro (CLR) y preestablecido (PR) (Figura 4). Estas pueden ser usadas para llevar el flip-flop a un estado definido desde su estado actual. Por ejemplo, la salida puede hacerse igual a 0 usando el pin CLR mientras que puede establecerse en 1 usando el pin PR. Sin embargo, estos pines pueden ser activos altos (Figura 4a) o activos bajos (Figura 4b) operados. Las formas de onda correspondientes al flip-flop JK disparado por el borde positivo con pines activos altos preestablecidos y claros se muestran en la Figura 5. Además, cabe señalar que estos pines pueden ser de naturaleza síncrona o asíncrona, lo que significa que las operaciones de ajuste y claro se producen dependiendo del reloj (mostrado por líneas verdes) o no (mostrado por líneas rojas), respectivamente. Además, si los pines preestablecidos y claros están activos en bajo, entonces los cambios observados en el diagrama se producen en el instante en que los pines claros y preestablecidos se ponen en bajo en lugar de en alto.