El mundo actual es, sin duda, un mundo electrónico lleno de diferentes tipos de sistemas que realizan diversos tipos de funciones. Estos sistemas necesitan comunicarse entre sí para lograr sus objetivos. Las acciones emprendidas por ellos dependen en gran medida de los datos recibidos/transmitidos por/de ellos. Digamos por ejemplo, supongamos que estamos aterrizando un avión y enviamos 0010000 al sistema para arrastrar las ruedas.

Ahora, imagina que nuestro patrón de bits se corrompe a lo largo del canal y es recibido por el sistema como 0010100. Esto podría causar que el sistema descarte su entrada (si es inválida) o realice una acción totalmente diferente a la prevista. En cualquiera de los casos, el resultado será el desastre, tal como nuestro único bit se alteró. Este ejemplo (bastante exagerado) indica la importancia de una comunicación de datos sin errores. Una forma de lograrlo es el uso de generadores de paridad y las damas.

La comprobación de la paridad es un método en el que se añade un bit extra llamado bit de paridad, normalmente en el MSB, del flujo de datos que debe ser transmitido. Ahora, ¿cómo decidir si se añade 1 o 0? Esto depende de si deseamos tener paridad impar o paridad par.

Paridad impar

Este es el caso en que el número de unos en el flujo de bits enviado (bits de datos en conjunción con el bit de paridad) tiene que mantenerse como un número impar. Es decir, supongamos que tenemos nuestro flujo de bits como 1001011, entonces la paridad se generaría como 1 de tal manera que el número de unos en el flujo de bits resultante (= 11001011) es 5, un número impar. Razonando de manera similar, podemos decir que para la secuencia de datos de 1001010, el bit de paridad debería ser necesariamente 0.

Paridad paritaria

En caso de que optemos por la paridad par, debemos asegurarnos de que el número total de unos en el flujo de bits, incluido el bit de paridad, se convierta en un número par. Por ejemplo, si la cadena de datos es 1001011, entonces el bit de paridad sería 0; mientras que si es 1001010, entonces el bit de paridad debería ser 1.

Ahora, intentemos diseñar un circuito digital que nos ayude a generar nuestro bit de paridad.

Generador de paridad impar

Asumamos que tenemos una secuencia de datos de tres bits (B2B1B0) que debe ser comunicada. La tabla I muestra los bits de paridad (OP) que debe ser generado por nuestro circuito para cada combinación de bits de entrada.

Tabla I

| B2 | B1 | B0 | OP |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

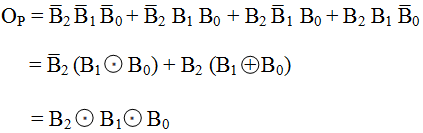

A partir de esto, podemos encontrar la expresión para P en términos de B2, B1 y B0 como

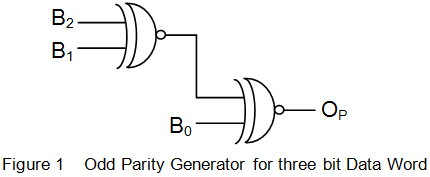

Esto significa que podemos construir un generador de paridad impar para tres bits de palabra de datos usando dos Puertas XNOR. El diseño realizado es el que se muestra en la figura 1.

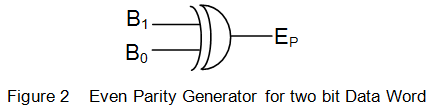

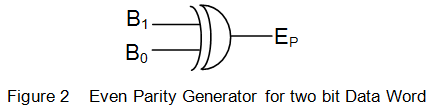

Generador de paridad uniforme

Diseñemos ahora una paridad uniforme (EP) generador de datos de dos bits de la palabra B1B0. La tabla de verdad asociada es la que se muestra en la Tabla II.

Tabla II

| B1 | B0 | EP |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Así que tenemos

Esto lleva al circuito digital como se muestra en la figura 2.

Este tipo de generación de paridad se emplea en los autobuses SPI y en las transmisiones UART.