Hemos visto un circuito sumador paralelo construido usando una combinación en cascada de víboras completas en el artículo Víbora paralela. De la misma manera, en el artículo sobre Sustractor paralelo hemos visto dos formas diferentes en las que se puede diseñar un sustractor paralelo de n bits. Sin embargo, siempre desde el punto de vista de la optimización, preferimos usar un solo circuito para realizar múltiples tipos de operaciones. Esto significa que en nuestro caso, tenemos que pensar si es posible realizar tanto la suma de n bits como la resta de n bits utilizando un único circuito digital, es decir, un sumador o sustractor paralelo circuito.

La respuesta es sí. Esto es porque, el proceso de sustracción de números binarios no es nada más que su complemento de 2s.

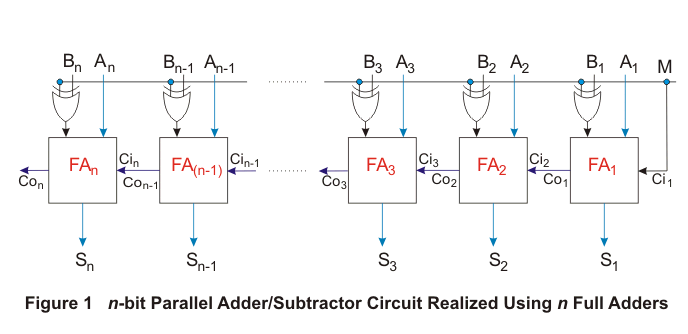

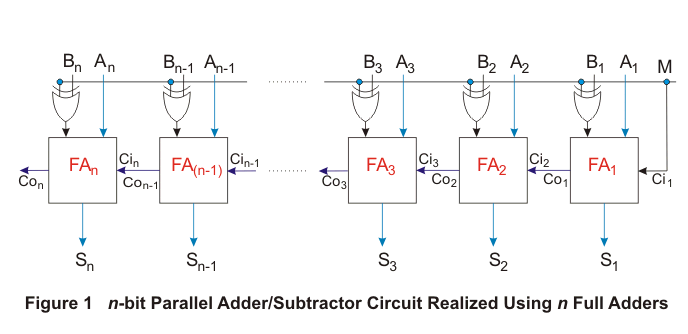

De ahí el diseño de la víbora paralela cuando se manipula de forma que proporciona la 2s complemento del número siempre que sea necesario puede ser usado como un sumador-sustractor paralelo. Uno de esos diseños realizado utilizando el Puertas XOR es como se muestra en la figura 1.

Aquí la línea M actúa como una línea de control, es decir, dependiendo del valor proporcionado en M, el circuito se comporta como un sumador o como un restador. La razón de esto puede explicarse a continuación. Supongamos que, si la línea M se conduce a bajo, entonces una de las entradas de todas y cada una de las puertas XOR sería el 0 lógico. Esto significa que las salidas XOR en este caso serán bits binarios inalterados del número

De manera similar, analicemos ahora el caso en el que M = 1, que significa que la línea de control de M se tira hacia arriba. En este caso, una de las entradas de cada Puerta XOR sería la lógica 1. Esto significa que obtenemos el complemento de los bits

Esto indica que el número binario se complementa antes de ser alimentado como una entrada para cada uno de los sumadores completos del circuito. Además, para el mismo caso, incluso el Ci1 de la primera víbora completa FA1 sería lógicamente alto. Como resultado, la disposición en cascada de sumas completas que se muestra en la figura 1 realiza efectivamente una sustracción binaria de bits en la que el número binario

Desventaja de la suma o resta paralela

Como la arquitectura de sumador o sustractor paralelo es muy similar a la de un víbora paralela (y también a la de un sustractor paralelo), incluso este diseño es propenso al efecto del retardo de propagación de las ondas. Sin embargo, este tipo de circuitos encuentra su aplicación en el campo de las computadoras como parte de la unidad aritmética y lógica (ALU), ayudando a numerosos cálculos.