Transistores de efecto de campo de unión (JFET) son un tipo de FET (dispositivos de alta impedancia de entrada) que tienen tres terminales, a saber, Fuente (S), Puerta (G) y Drenaje (D). Estos dispositivos también se denominan dispositivos de voltaje controlado como el voltaje aplicado en el terminal de la puerta determina la cantidad de corriente que fluye entre el drenaje y los terminales de la fuente. Las FETs pueden estar compuestas por pn- o Schottky-junction debido a que se llaman pn JFETs o Metal Semiconductor FETs (MESFETs), respectivamente. Además, las FETs de pn pueden clasificarse en dos tipos, a saber, (i) n-canal JFET y ii) Canal p JFETdependiendo de si el actual el flujo se debe a los electrones o a los agujeros, respectivamente.

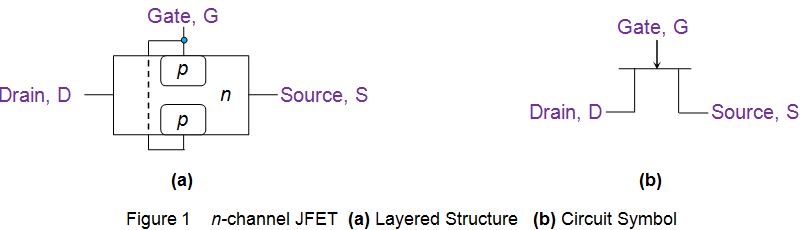

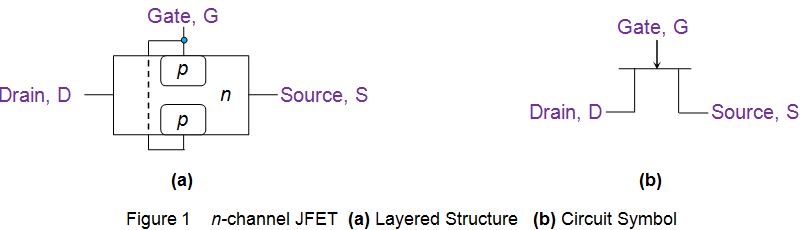

n-canal JFET

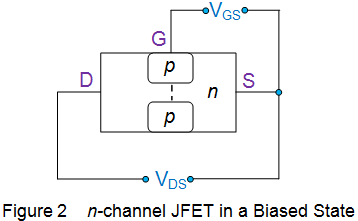

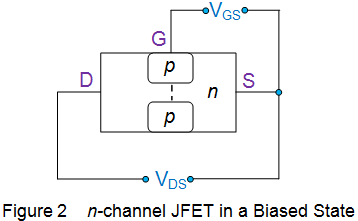

El esquema de un JFET de n canales junto con su símbolo de circuito se muestra en la Figura 1. De la estructura en capas mostrada por la Figura 1a, está claro que el JFET de n canales tiene su mayor parte hecha de semiconductor tipo n. Las dos caras mutuamente opuestas de este material a granel de la fuente y las terminales de drenaje. Además, también se ve que hay dos p-regiones relativamente pequeñas incrustadas en este sustrato que se unen internamente para formar la terminal de la puerta. Así, aquí, la fuente y los terminales de drenaje son de tipo n mientras que la puerta es de tipo p. Debido a esto, dos uniones de pn se formará dentro del dispositivo, cuyo análisis revela el modo en que el JFET funciona. Además, el símbolo del circuito mostrado en la Figura 1b tiene una flecha que apunta hacia el dispositivo en su terminal de la Puerta que indica la dirección en la que la corriente fluirá, siempre que la unión pn esté sesgada hacia adelante.

Funcionamiento del JFET de n canales

En el JFET de n canales, la mayoría de los portadores de carga serán los electrones, ya que el canal formado entre la fuente y el drenaje es de tipo n. Además, el funcionamiento de estos dispositivos depende de los voltajes aplicados en sus terminales (Figura 2).

Caso I: Considere el caso en el que no voltaje se aplica al dispositivo, es decir, VDS = 0 y VGS = 0. En este estado, el dispositivo estará inactivo y no actual fluye a través de él, es decir, yoDS = 0.

Caso II: Ahora considere que el terminal de drenaje del dispositivo está conectado al terminal positivo de la batería mientras que su negativo está conectado a la fuente, es decir, VDS = +ve. Sin embargo, dejemos que la terminal de la puerta permanezca en estado imparcial, lo que significa que VGS = 0. En este instante, los electrones dentro del n-sustrato del dispositivo comienzan a moverse hacia el drenaje siendo atraídos por la fuerza positiva ejercida por el batería. Al mismo tiempo, el electrón también será repelido de la fuente al estar conectado al terminal negativo del suministro de voltaje. Esto da como resultado un flujo neto de corriente desde el desagüe hasta la fuente (según la dirección convencional) cuyo valor sólo se ve restringido por la resistencia que le ofrece el canal.

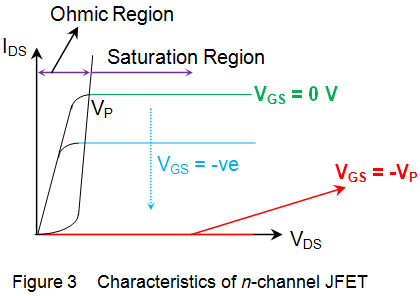

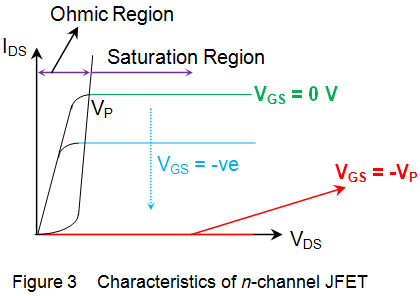

Además, se observa que el aumento de VDS aumenta la corriente que fluye a través del dispositivo en un estado inicial que se puede denominar como la región óhmica de los JFET. Sin embargo, cabe señalar que el aumento de VDS también causa un aumento en el ancho de las regiones de agotamiento que rodean las uniones de pn. Esta inturnidad hace que el ancho del canal se reduzca, aumentando así su resistencia. Este fenómeno continúa hasta que ambas regiones de agotamiento crecen hasta un punto en el que casi parecen tocarse entre sí, condición que se conoce como «pinch-off». El valor correspondiente de VDS se conoce como voltaje de pinchazo, VP. Sin embargo, incluso en este caso, existe un canal estrecho con alta densidad de corriente dentro del dispositivo, debido a que el IDS se saturará hasta un nivel de IDSS como se indica en la figura 2. Es este comportamiento de la JFET lo que hace que se comporte como una fuente de corriente constante.

Caso III: A continuación, para la configuración descrita en el caso II, vamos a añadir el fuente de tensión en el terminal de la puerta, de tal manera que la puerta es una fuente de w.r.t. negativa, es decir, VGS = -ve while VDS es +ve. En este caso, el dispositivo se comporta de una manera muy similar a la del caso II, pero para un valor menor de VDS. Esto significa que el pinchazo y la saturación ocurren bastante antes y se deciden por el potencial negativo aplicado en la puerta, es decir, más negativa la VGSantes el pinchazo debido a que antes será la saturación, reduciendo la IDSS (Figura 3).

A medida que el fenómeno continúa, se ve que surge una condición en la que el nivel de saturación de la corriente de drenaje a la fuente IDS se produce justo para un valor de 0 mA. Esto significa que no hay actual fluya a través del dispositivo y esencialmente el dispositivo se apagará. El valor de VDS por lo cual esto no será nada más que el voltaje negativo de pellizco, es decir, VDS = -VP.

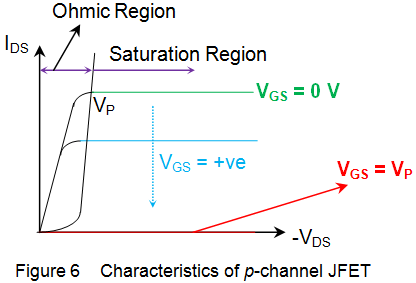

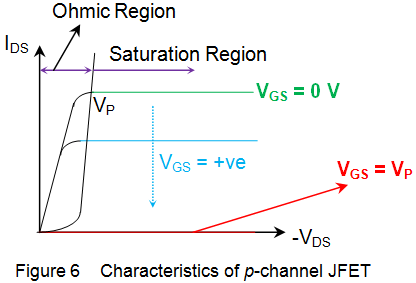

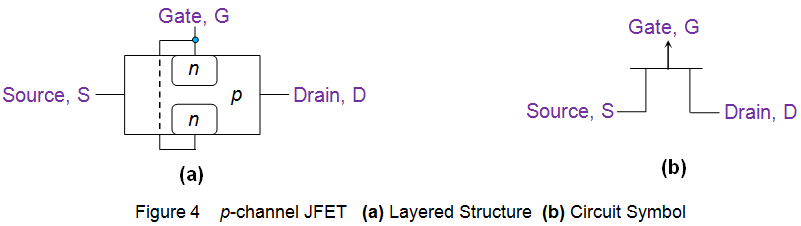

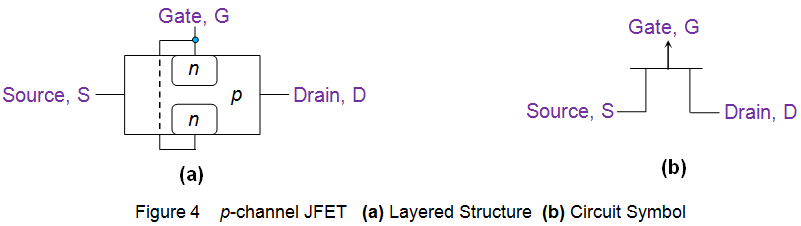

Canal p JFET

El Canal p JFET (Figura 4a) exhibe el modo de funcionamiento que es similar al de su contraparte, el n-canal JFET excepto algunas diferencias. En el caso de Canal p JFETla mayor parte del dispositivo es de tipo p, en el que están incrustadas las dos pequeñas regiones de tipo n. Por lo tanto, tiene un terminal de puerta de tipo n y una fuente y drenaje de tipo p, lo que hace que el canal sea de tipo p donde los agujeros serán la mayoría carga los portadores. A continuación, la dirección de la flecha en su símbolo de circuito está apuntando hacia fuera, a diferencia de lo que ocurre en el caso de los JFET de n canales (Figura 4b).

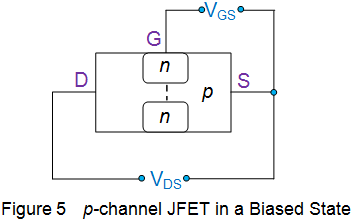

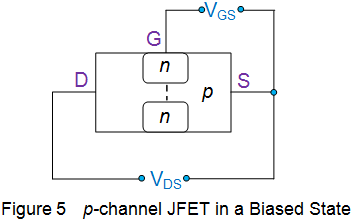

Funcionamiento del canal p del JFET

Al igual que en el caso de los JFET de n canales, el funcionamiento de estos dispositivos también depende de la voltajes aplicado en sus terminales (Figura 5).

Caso I: Si VDS = 0 y VGS = 0, el dispositivo estará inactivo sin corriente, es decir, IDS = 0.

Caso II: Ahora considera que VDS para ser ve mientras que VGS es 0. En este estado, la corriente fluye desde la fuente hacia el desagüe (según la dirección convencional) ya que los agujeros dentro del p-sustrato se mueven hacia el desagüe mientras son repelidos de la fuente. El valor de esta corriente está restringido sólo por la resistencia del canal y se ve que aumenta con una disminución de VDS (Región óhmica). Sin embargo, una vez que se produce el pinchazo (VDS = VP), el actual IDS se satura a un nivel particular IDSSdurante el cual el dispositivo actúa como una fuente de corriente constante (Figura 6).

Caso III: A continuación, que VGS = +ve mientras que VDS es -ve. Aquí el efecto exhibido es similar al del caso II con el hecho de que la saturación se produce a un ritmo más rápido que el VGS se vuelve más y más positiva. Similar a lo visto en n-canal JFETsincluso aquí la corriente deja de fluir ya que el valor de VDS se convierte en igual a VP…convirtiendo el dispositivo en un estado de apagado.